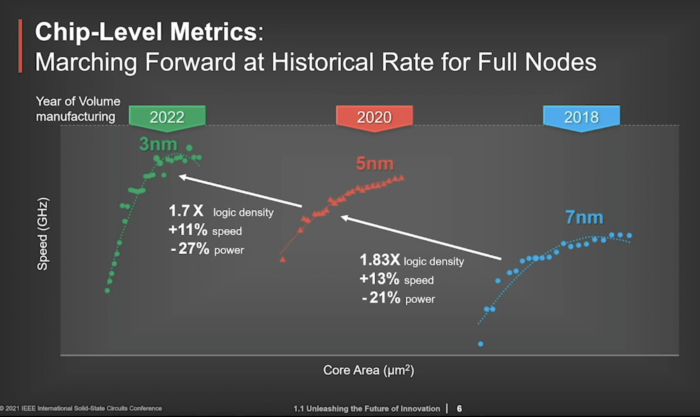

台积电董事长刘德音(Dr. Mark Liu)证实,该公司的下一代 3nm 芯片制造节点,正在按计划推进之中。作为全球知名的芯片代工制造商,台积电当前正在建设 3nm 生产线,且有望明年转入试生产。与 5nm 制程节点相比,3nm 可提供几乎翻番的逻辑密度,辅以 11% 的性能提升、或 27% 的能效改进。

3nm 较 5nm 制程的增益示例(图 via WCCFTech)

台积电高管在早前的国际固态电路会议(ISSCC)演讲期间的这番表态,证实了该公司对下一代制造技术的信心。

在满足当前和未来产品的日益增长需求的同时,即便汽车领域的产品需求有所提升,也不会对整体产能造成太大影响。

需要指出的是,部分媒体误解了所谓的“3nm 工艺提前”。毕竟在主题为《释放创新未来》的 27 分钟演讲期间,高管并未直言此事,仅在开头和结尾对 3nm 开发进度“顺口一提”。

为提升逻辑密度,需要对相关技术展开协同优化,同时也增加了一定的成本。

除了透露 3nm 技术的发展正在如期推进且相当顺利,刘德音还提供了对 3nm 工艺的最新数据、以及对工艺发展的看法。

他指出,到目前为止,台积电已出货约 18 亿片基于 7nm 工艺节点的芯片。截止 2020 年,该公司一直是行业中的领跑者。

得益于极紫外光刻(EUV)技术,台积电能够实现更高的保真度、缩短周期、并降低工艺的复杂性和缺陷率。

值得一提的是,台积电在 5nm 节点的十层掩模工艺中使用了 EUV 技术(具体包括线切割、接触、金属线图案),并用单层 EUV 取代了早期的多层深紫外(DUV)工艺。

随后刘德音强调了设计技术的协同优化(DTC),以及该方案在过去几年中对芯片制造的重要性。对于芯片制造商来说,这使得他们能够同时使用设计和制造技术来满足性能要求。

此外 DTCO 使得台积电在衡量节点的逻辑密度时超越了固有的缩放指标,比如接触栅间距和最小金属间距。

结合有源区上的栅极接触、单扩散中断、鳍片减少等特性,还可为 3nm 工艺节点带来 1.8 倍于 5nm 的逻辑密度。

最后,刘德音披露了公司的未来计划,包括开发 sub-3D 材料和晶圆级单晶六方氮化硼。

两者的特点是能够在较低的制造温度下,转移至任意衬底上,从而为在三个维度上制造有源逻辑层和存储层开辟了新的道路。

此外台积电对于低维材料的研究,包包括一维的碳纳米管。借助这一晶体通道的关键,是开发出一种栅极长度较短的晶体管介电材料。

如上图所示,研究表明这项技术已有实现的可能。具有高k栅极堆叠能力的新材料,很适合用于制造栅极长度为 10nm 的晶体管。

当然,为了达成如此远大的目标,台积电还需要与芯片行业的所有同行紧密合作,以确保 3nm 工艺能够发展到 2 倍于当前的性能。

考虑到该公司正在量产的 5nm 顺应了这一趋势,即将面世的 3nm 节点也有望遵循这一时间安排。

特别提醒:本网内容转载自其他媒体,目的在于传递更多信息,并不代表本网赞同其观点。其原创性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺,并请自行核实相关内容。本站不承担此类作品侵权行为的直接责任及连带责任。如若本网有任何内容侵犯您的权益,请及时联系我们,本站将会在24小时内处理完毕。

台积电3nm工艺或

台积电3nm工艺或 2021年筋膜枪品牌

2021年筋膜枪品牌 玖富数科 以数字

玖富数科 以数字 红魔 6 预热:暗示

红魔 6 预热:暗示 三星显示宣布加入

三星显示宣布加入 苹果 microLED 相

苹果 microLED 相 苹果向开发者提供

苹果向开发者提供 谷歌将为安卓手机

谷歌将为安卓手机 目前最好用的5款

目前最好用的5款 社群团购&直播货

社群团购&直播货 门店业务持续高涨

门店业务持续高涨 2021年最值得入手

2021年最值得入手 小容语音机器人再

小容语音机器人再 致渠道合作伙伴:齐

致渠道合作伙伴:齐